2026/01/23(金)USB Blasterのクローン

JTAG Blaster

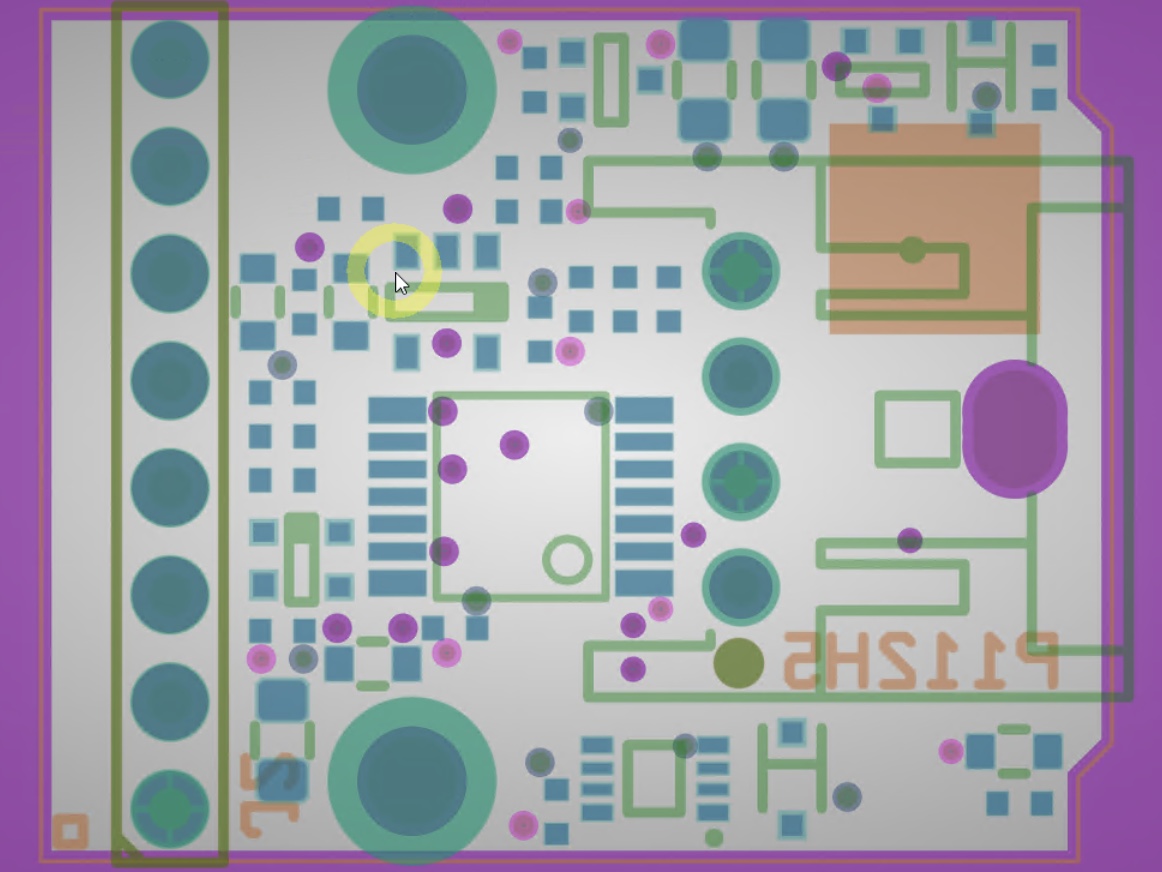

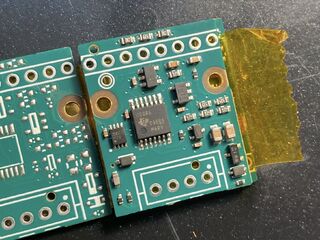

製品名 EPT-2232H-SP-S1 29.99USDEarthPeopleTechnology

https://earthpeopletechnology.com/?wpsc-product=ept-2232h-sp-s1

Altera USB BlasterのJTAG制御プロトコル

出典: https://github.com/swetland/jtag/blob/master/usb-blaster-protocol.txt

_________

| |

| AT93C46 |

|_________|

__|__________ _________

| | | |

USB__| FTDI 245BM |__| EPM7064 |__JTAG (B_TDO,B_TDI,B_TMS,B_TCK)

|_____________| |_________|

__|__________ _|___________

| | | |

| 6 MHz XTAL | | 24 MHz Osc. |

|_____________| |_____________|

Quoting from ixo.de (http://www.ixo.de/info/usb_jtag/)usb_jtag/device/c51/usbjtag.c comments:

usb_jtagファームウェアは現在、AlteraのUSB-BlasterにおけるFT245BMとAlteraプログラム済みEPM7064 CPLDの組み合わせと全く同じ動作をします。

CPLDは主に2つのモードを認識します:ビットバンギングモードとバイトシフトモードです。

起動時はビットバンギングモードで動作します。ホストからEP2OUT(Endpoint 2 OUT)経由でバイトを受信する際、各バイトBは以下のように処理されます:

ビットバンギングモード

1. Bのビット6(0x40)を「読み取りビット」として記憶する。2. ビット7(0x80)が設定されている場合、続くXバイト(X := B & 0x3F)に対してバイトシフトモードに切り替え、現時点では他の処理を行わない。

3. そうでない場合、JTAG信号を以下のように設定する:

- ビット0が設定されている場合(0x01)、TCK/DCLKをハイ、それ以外はロー

- ビット1が設定されている場合(0x02)、TMS/nCONFIGをハイ、それ以外はロー

- ビット2が設定されている場合(0x04)、nCEをハイ、それ以外はロー

- ビット3が設定されている場合(0x08)、nCSをハイ、それ以外はロー

- ビット4が設定されている場合(0x10)、TDI/ASDI/DATAOをハイ、それ以外の場合ロー

- ビット5が設定されている場合(0x20)、出力有効/LEDをアクティブ、それ以外の場合ロー

4. 「リードビット」(0x40)が設定されていた場合、TDO(CONF_DONE)および

DATAOUT/(nSTATUS)ピンの状態を記録し、バイト( (DATAOUT<<1)|TDO)として

出力FIFOからホストへ送信する。

バイトシフトモード

1. ホストからのバイトをシフトレジスタにロード2. 8回実行する(バイトの各ビットごとに;shift.a51で実装)

- nCS=1の場合、TDOからキャリービットを設定、それ以外の場合DATAOUTからキャリービットを設定 (アクティブシリアルモード)

- キャリービットを含めてシフトレジスタをローテート

- TDI := キャリービット

- TCKを上昇、その後TCKを下降