2021/04/06(火)LPC55xx DMA : Trigger operational detail

参照: NXP LPC55S1x RM R1.3, 22.5.1.3項 *1

Trigger operational detail

DMAチャンネルで転送を開始するには、必ず何らかのトリガが必要です。トリガには、ハードウェアトリガとソフトウェアトリガがあり、いくつかの方法で使用できます。

SWTRIGビットが0に設定されているチャンネルは、ハードウェアまたはソフトウェアによってトリガをかけることができます。ソフトウェアトリガは,SETTRIGレジスタの該当ビットに1を書き込むことで実現します。ハードウェアトリガの場合は、関連するチャネルのCFGレジスタのHWTRIGEN、TRIGPOL、TRIGTYPE、TRIGBURSTフィールドの設定が必要です。チャネルの初期設定時に、XFERCFGレジスタのSWTRIGビットを設定すると、直ちに転送が開始されます。

関連するCFGレジスタのPERIPHREQENビットが設定されていれば、チャネル上の転送はDMAリクエストのペースに合わせて行われます。それ以外の場合は、全速力で転送が行われます。

CTLSTATレジスタのTRIGビットは、XFERCFGレジスタの値CLRTRIG(ビット0)によって決定される転送の終了時にクリアすることができます。CLRTRIGに1があると、ディスクリプタが使い果たされたときにトリガがクリアされます。

2021/04/04(日)NXP MCU公式トピック(LPC、Kinetis、etc.)

LPC5500 Series

- Arm® Cortex®-M33 based Microcontroller Series for Mass Market, Leveraging 40nm Embedded Flash Technology 記事

- MCU Tech Minutes 動画

- Exploring the SCTimer Feature on LPC5500 Series MCUs.

- (placeholder)

LPC551x Family

LPC552x Family

- NXPのCortex-M33ベースMCU、第2弾はメインストリーム製品 記事

Kinetis KE1xZ Family

- 耐水タッチ機能統合の5Vマイクロコントローラー 記事

Kinetis K32 L2/L3 Family

- NXP、K32 L3シリーズ・マイクロコントローラを量産開始:消費電力を低減し、インダストリアルIoTセンサ・ノードに対応 記事

2021/03/28(日)LPC551x/S1x データシート : 概要と特長

参照: NXP LPC55S1x PDS R1.4, 1章~2章 *1

概要

LPC55S1x/LPC551xは、ARM Cortex-M33ベースの組み込みアプリケーション用マイクロコントローラです。これらのデバイスには、CASPER Cryptoエンジン、最大256KBのオンチップフラッシュ、最大96KBのオンチップSRAM、オンザフライでフラッシュを暗号化/復号化するPRINCEモジュール、コードウォッチドッグ、High-speed/Full-speedのUSBホストおよびデバイスインターフェース(Full-speedの場合はクリスタルレス動作)、CAN FD、5つの汎用タイマ、1つのSCTimer/PWM、1つのRTC/アラームタイマ、1つの24ビットマルチレートタイマ(MRT)、Windowed Watchdog Timer(WWDT)、9つのフレキシブルなシリアル通信ペリフェラル(USART、SPI、高速SPI、I2C、またはI2Sインターフェースとして構成可能)、プログラマブルロジックユニット(PLU)、同時変換が可能な1つの16ビット2.0Msps ADC、コンパレータ、温度センサを搭載しています。

ARM Cortex-M33は、TrustZone®テクノロジーにより、貴重なIPやデータを保護するアイソレーション機能を備えたセキュリティ基盤を提供します。また、デジタル信号処理(DSP)命令を内蔵しているため、デジタル信号制御システムの設計やソフトウェア開発を容易にします。また、LPC55S1x/LPC551xは、セキュリティ要件をサポートするために、セキュアブート、HASH、AES、RSA、UUID、ダイナミック暗号化・復号化、デバッグ認証、TBSAコンプライアンスをサポートしています。

特長とメリット

- ARM Cortex-M33コア(r0p4)を搭載

- CASPER Cryptoコプロセッサは、楕円曲線暗号(Elliptic Curve Cryptography、ECC)などの特定の非対称暗号アルゴリズムに必要な様々な機能のハードウェアアクセラレーションを可能にするために提供されます。

- オンチップメモリ

- 最大256KBのオンチップフラッシュプログラムメモリ、フラッシュアクセラレータ、512バイトのページ消去・書き込みが可能。

- 最大96KBのSRAM(コードバス上の16KB SRAM、システムバス上の最大64KBのSRAM(連続した64KB)、およびシステムバス上の16KB USB SRAMで構成され、USBインターフェースや汎用的な用途に使用することができます。

- PRINCEモジュールは、オンチップフラッシュに書き込まれるデータをリアルタイムに暗号化し、暗号化されたフラッシュデータを読み出し時に復号化することで、アプリケーションコードなどの資産の保護を可能にし、セキュアなフラッシュアップデートを可能にします。

- オンチップROMブートローダを搭載

- オンチップフラッシュからのイメージの起動

- CRC32によるイメージ・インテグリティ・チェックに対応

- インシステムプログラミング(ISP)コマンドによるフラッシュプログラミングに対応:以下のインターフェースを使用します。HIDクラスのデバイスを使用したUSB0/1インターフェース、自動ボーレートのUARTインターフェース(Flexcomm 0)、モード3(CPOL=1、CPHA=1)を使用したSPIスレーブインターフェース(Flexcomm 3または8)、I2Cスレーブインターフェース(Flexcomm 1)。

- ROM API機能。フラッシュプログラミングAPI、電源制御API、NXP Secure BootファイルフォーマットVer.2.0(SB2ファイル)を用いたセキュアファームウェアアップデートAPI。

- PRINCE暗号化フラッシュ領域からのイメージのブートをサポート

- NXPデバッグ認証プロトコル バージョン1.0 (RSA-2048)および1.1 (RSA-4096)をサポート

- デバッグ認証によるシールドパートのFault Analysisモードへの移行に対応

- セキュアブートをサポート

- RSASSA-PKCS1-v1_5シグネチャとSHA256ダイジェストを暗号化署名の検証に使用しています。

- RSA-2048ビット公開鍵(2048 bit modulus, 32-bit exponent)に対応

- RSA-4096ビットの公開鍵(4096 bit modulus, 32-bit exponent)に対応

- イメージ公開鍵の検証にx509証明書フォーマットを採用

- 最大4つの取消可能なRoot of Trust(RoT)または認証局キーをサポート。4つのRoT公開鍵のSHA-256ハッシュダイジェストを保護されたフラッシュ領域(PFR)に格納することで、Root of Trustを確立。

- イメージキーリボケーションによるロールバック防止機能をサポートし、x509証明書のシリアルナンバーフィールドを利用した最大16個のイメージキー証明書のリボケーションをサポート。

- シリアルインターフェース

- Flexcomm Interfaceには、最大9つのシリアル周辺回路が含まれます(Flexcomm Interface 0~7およびFlexcomm Interface 8)。各Flexcomm Interface(高速SPI専用のFlexcomm 8を除く)は、USART、SPI、I2C、I2Sの各インターフェースをソフトウェアで選択できます。各Flexcomm Interfaceには、USART、SPI、I2SをサポートするFIFOが搭載されています。各Flexcomm Interfaceには、共有フラクショナルボーレートジェネレータやタイムアウト機能など、さまざまなクロックオプションが用意されています。Flexcomm 0~5はそれぞれ1チャネルペアのI2Sを、Flexcomm 6~7はそれぞれ4チャネルペアのI2Sを提供します。

- I2Cバスインターフェースは、Fast-modeおよびFast-mode Plusに対応し、最大1Mbit/sのデータレートで、複数のアドレス認識とモニタモードを備えています。また、2組のトゥルーI2Cパッドは、スレーブとしてHigh-speedモード(3.4Mbit/s)に対応します。

- USB 2.0フルスピードホスト/デバイスコントローラは、オンチップPHYと専用DMAコントローラを搭載し、テクニカルノート(TN00065)に記載されているソフトウェアライブラリの例を参考に、デバイスモードでのクリスタルレス動作をサポートしています。

- オンチップHS PHYを備えたUSB 2.0ハイスピードホスト/デバイスコントローラ

- デジタル周辺機能

- (割愛)

- セキュリティ機能

- ARM TrustZone®に対応

- AES-256暗号化/復号化エンジンは、PUFまたはソフトウェアから供給された鍵を直接使用可能です。

- セキュアハッシュアルゴリズム(SHA2)モジュールは、専用のDMAコントローラを使用したセキュアブートをサポートします。

- PUF(Physical Unclonable Function)は、シリコンフィンガープリント用の専用SRAMを使用。PUFは、64~4096ビットの鍵の生成、保存、再構築が可能。鍵抽出用のハードウェアも含まれています。

- True Random Number Generator(TRNG)

- 識別のための128ビットのデバイス固有のシリアル番号(UUID)

- セキュアGPIO

- コードフローの整合性を検出するコードウォッチドッグ

- タイマ

- (割愛)

- アナログ周辺機能

- 5つの差動チャネルペア(または10のシングルエンドチャネル)を持つ16ビットADCは、複数の内部および外部トリガ入力を備え、最大2.0MSamples/secのサンプルレートを実現します。ADCは、差動ペアに属する2つのADC入力チャネルの同時変換をサポートしています。

- ADCに接続された温度センサを内蔵

- 5つの入力端子と外部または内部基準電圧を備えたコンパレータ

- クロック生成

- (割愛)

- 省電力モードとウェイクアップ

- PMU(Power Management Unit)を内蔵し、消費電力を最小限に抑えます。

- 省電力モード:スリープ、ディープスリープ(RAM保持)、パワーダウン(RAM保持とCPU保持)、ディープパワーダウン(RAM保持)。

- ペリフェラルの割り込みによるウェイクアップオプションを設定可能。

- ウォッチドッグオシレータから動作するマイクロティックタイマと、32.768kHzのクロックから動作するリアルタイムクロック(RTC)を、スリープおよびディープスリープモードからの復帰に使用することができます。

- パワーオンリセット(POR)(約0.8V)

- VBAT_DCDCのブラウン・アウト検出器(BOD)は、強制リセットのための個別のしきい値を備えています。

- 内蔵のDC-DCコンバータで動作

- 1.8V~3.6Vの単一電源に対応

- JTAGバウンダリスキャンをサポート

- 動作温度範囲 -40 °C ~ +105 °C

- HLQFP100、VFBGA98、HTQFP64の各パッケージで提供

2021/03/28(日)LPC55xx DMA Register : Set valid register

参照: NXP LPC55S1x RM R1.3, 22.6.13項 *1

Set valid register

SETVALID0(set valid 0)レジスタでは、1つまたは複数のDMAチャネルのCTRLSTATレジスタのVALIDビットをセットすることができます。VALIDビットの説明については、22.6.17項「Channel transfer configuration registers」を参照してください。このレジスタは書き込み専用です。

CFGVALIDビットおよびSV(set valid)ビットは、ソフトウェアによるより直接的なDMAブロックタイミング制御を可能にします。一連のディスクリプタの中の各チャネルディスクリプタは、CFGVALIDビットの設定またはチャネルのSETVALIDフラグの設定によって有効にすることができます。

通常、CFGVALIDビットはセットされています。これにより、DMAはチャネルディスクリプタがアクティブであり、実行可能であることを伝えます。DMAは、CFGVALIDビットがセットされたディスクリプタブロックを、ソフトウェアの介入なしに順次実行していきます。

CFGVALIDビットを0に設定したままにしておくと、ソフトウェアが継続をトリガするまで、DMAシーケンスをディスクリプタで一時停止させることができます。DMA送信中に、CFGVALIDが0に設定されたチャネルディスクリプタが見つかった場合、DMAは(以前にバッファリングされた)SETVALID0のそのチャネルに対するフラグをチェックします。見つかった場合、DMAはディスクリプタを有効に設定し、SVビットをクリアし、ディスクリプタの処理を再開します。それ以外の場合、DMAはチャネルのSETVALID0ビットがセットされるまで一時停止します。

2021/03/27(土)LPC55xx I2S : FIFO buffer configurations and usage

参照: NXP LPC55S1x RM R1.3, 37.8.4項 *1

FIFO buffer configurations and usage

Flexcomm Interfaceは、処理されるデータのサイズに応じて、いくつかのデータパック/アンパックの実現性をサポートしています。FIFOの使用方法の詳細は、I2S Configuration register 1(CFG1)レジスタのDATALENフィールドの値と、その他のコンフィギュレーションビットによって決定されます。

DATALENに4~16のデータビット数を指定した場合

- FIFOは幅32ビット、深さ8エントリで構成されます。

- バスとFIFO間の各データ転送は、32ビットワードに収まる左右の値のペアになります。左と右のデータの順序は、RIGHTLOWコンフィギュレーションビットで選択できます。

- ONECHANNEL = 1でチャネルペアを構成した場合、転送されるのは1つの値のみで、公称では左の値となります。

DATALENに17~24のデータビット数を指定した場合

- この場合、FIFOは幅48ビット、深さ8エントリで構成されます。

- バスとFIFO間のデータ転送は、PACK48コンフィギュレーションビットおよびDMAが有効かどうかによって異なります。

- DMAが有効な場合、すべての転送はFIFOWRまたはFIFORDで行われます。DMAが有効でない場合は、I2S機能で選択されたデータ方向に応じて、FIFOWRまたはFIFORDとFIFOWR48HまたはFIFORD48Hで交互に転送されます。

- いずれの場合も、2回の転送で左右の値のペアが構成されます。左と右のデータの順序は、RIGHTLOWコンフィギュレーションビットで選択できます。

- PACK48 = 0の場合、2つの転送はいずれも17~24ビットのデータを定義します。PACK48 = 1の場合、最初の転送では32ビットのデータが提供され、2回目の転送では定義されたペアデータを完成させるために必要な残りのデータが提供されます。

- チャネルペアがONECHANNEL = 1で構成されている場合は、FIFOWRまたはFIFORDレジスタを使用して左の値のみが転送されます。

DATALENに25~32のデータビット数を指定した場合

- この場合、FIFOは幅32ビット、深さ8エントリで構成されます。

- バスとFIFOの間の各データ転送は、左から右の順に1つの値となります。

- ONECHANNEL = 1でチャネルペアを構成した場合は、1つの値のみが転送されます。

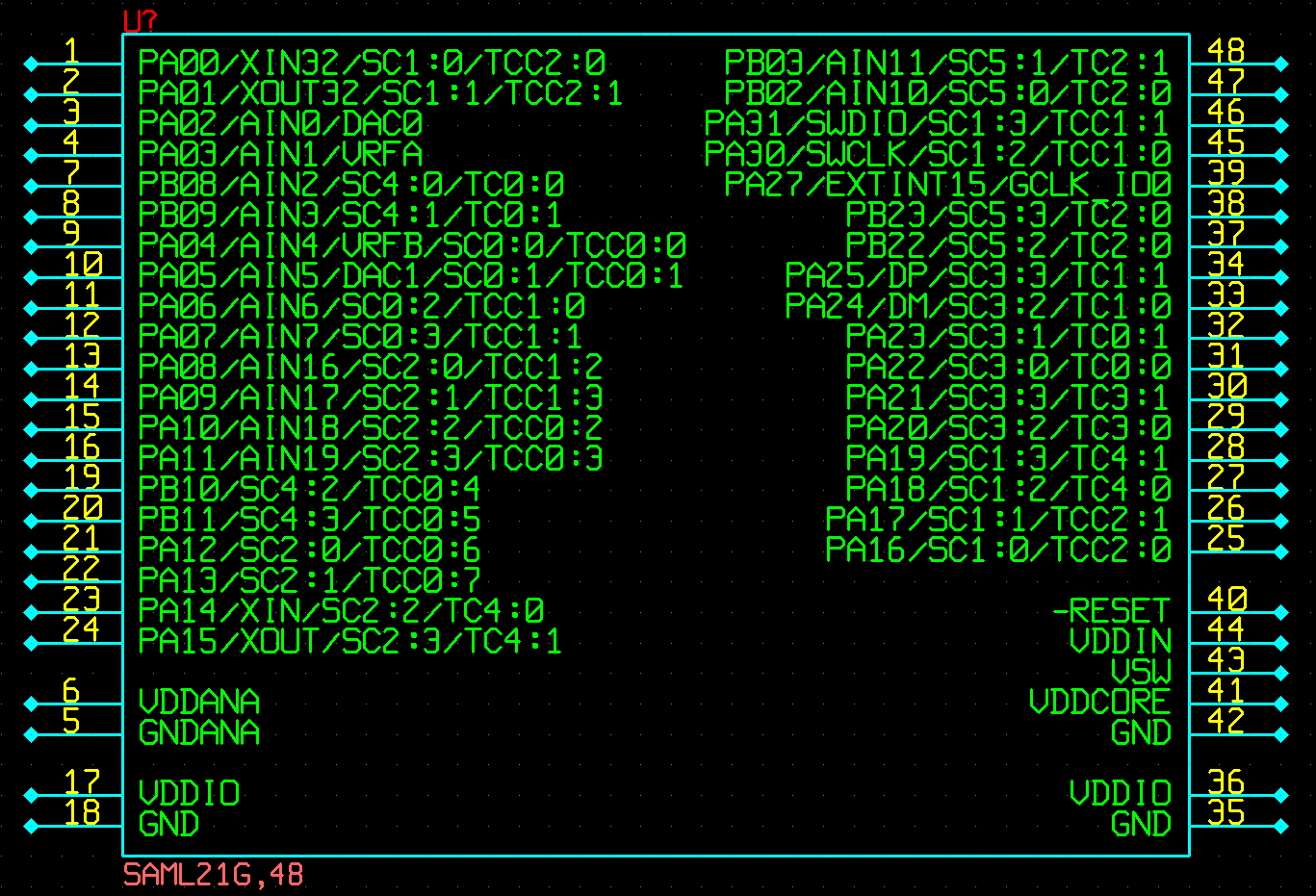

2021/02/17(水)Our SAML21 symbol for PCB Elegance

SAML21Gのシンボルが完成しました

ありがとうございました。

SAMマイコンの価格は値上がり傾向にあります。

CompareSAM.ods